The University of York Department of Computer Science

# Architectural and scalability issues in hardware synthesis of high-level languages

# **Qualifying Dissertation**

lan Gray

iang@cs.york.ac.uk

5th September 2007

#### Abstract

The proliferation of embedded systems over the last decade has increased the demands on system designers to create devices that are powerful and feature-rich whilst remaining reliable, cheap and energy-efficient. New technologies such as FP-GAs and high-density ASICs provide suitable implementation fabrics, but designer productivity has not increased accordingly and almost all designs are still created using low-level hardware description languages. To mitigate this problem, hardware synthesis systems have been developed that attempt to translate high-level software languages like C or Ada into an implementable hardware description. Whilst the resulting increase in abstraction allows for more rapid development, current synthesis techniques do not scale to allow the efficient creation of large designs. The designer lacks control over the implementation architecture and cannot influence the synthesis process. As a result, the use of high-level synthesis is currently limited to prototyping or to the specification of small subcomponents.

This document examines the use of FPGAs as an implementation platform and how they are related to the system-on-chip and network-on-chip design methodologies. It then discusses the current state of hardware synthesis and examines the problems that are encountered when using it. Techniques from the software domain are then detailed that may help to resolve some of these issues. Reflection, aspect-oriented programming, and metaobject protocols are considered.

# Contents

| 1 | Intro | oduction                                              | 4    |

|---|-------|-------------------------------------------------------|------|

| 2 | Lite  | rature Review                                         | 6    |

|   | 2.1   | Design of embedded systems                            | . 6  |

|   |       | 2.1.1 The System-on-Chip paradigm                     | . 7  |

|   |       | 2.1.2 From System-on-Chip to Network-on-Chip          | . 7  |

|   | 2.2   | Field-Programmable Gate Arrays                        | . 9  |

|   |       | 2.2.1 Advanced FPGA architectures                     | . 10 |

|   |       | 2.2.2 The FPGA design process                         | . 11 |

|   |       | 2.2.3 Partial Dynamic Reconfiguration                 | . 13 |

|   |       | 2.2.4 Applications of Partial Dynamic Reconfiguration | . 13 |

|   | 2.3   | Describing hardware with software                     | . 15 |

|   |       | 2.3.1 Hardware description languages                  | . 15 |

|   |       | 2.3.2 SystemC                                         | . 16 |

|   |       | 2.3.3 High-level language synthesis                   | . 17 |

|   |       | 2.3.4 Handel-C                                        | . 19 |

|   |       | 2.3.5 Other synthesised languages                     | . 21 |

|   |       | 2.3.6 Summary                                         | . 22 |

|   | 2.4   | Hardware/software codesign                            | . 23 |

|   |       | 2.4.1 Problems with codesign                          | . 25 |

|   | 2.5   | Reflection                                            | . 26 |

|   |       | 2.5.1 Smalltalk                                       | . 28 |

|   | 2.6   | Metaobject protocols                                  | . 29 |

#### CONTENTS

| Bibliography 55 |                      |                                 |                                                   |    |  |  |  |  |

|-----------------|----------------------|---------------------------------|---------------------------------------------------|----|--|--|--|--|

|                 | 4.2                  | Contin                          | uing work                                         | 54 |  |  |  |  |

|                 |                      | 4.1.3                           | Question 3                                        | 53 |  |  |  |  |

|                 |                      | 4.1.2                           | Question 2                                        | 53 |  |  |  |  |

|                 |                      | 4.1.1                           | Question 1                                        | 52 |  |  |  |  |

|                 | 4.1                  | Research questions              |                                                   |    |  |  |  |  |

| 4               | Res                  | earch F                         | Proposal                                          | 51 |  |  |  |  |

|                 |                      | 3.2.6                           | Summary                                           | 49 |  |  |  |  |

|                 |                      | 3.2.5                           | Handel-C results                                  | 47 |  |  |  |  |

|                 |                      | 3.2.4                           | Handel-C description                              | 46 |  |  |  |  |

|                 |                      | 3.2.3                           | Ada results                                       | 45 |  |  |  |  |

|                 |                      | 3.2.2                           | Ada description                                   | 42 |  |  |  |  |

|                 |                      | 3.2.1                           | The desired architecture                          | 42 |  |  |  |  |

|                 | 3.2 Problem analysis |                                 |                                                   | 41 |  |  |  |  |

|                 | 3.1                  |                                 |                                                   |    |  |  |  |  |

| 3               |                      | eliminary work                  |                                                   |    |  |  |  |  |

| 2               | Drol                 | reliminary work 40              |                                                   |    |  |  |  |  |

|                 | 2.8                  | Conclu                          | usions                                            | 38 |  |  |  |  |

|                 |                      | 2.7.3                           | Other AOP implementations                         | 38 |  |  |  |  |

|                 |                      | 2.7.2                           | AspectJ                                           | 36 |  |  |  |  |

|                 |                      | 2.7.1                           | Aspect-Oriented Programming                       | 35 |  |  |  |  |

|                 | 2.7                  | The inheritance anomaly and AOP |                                                   |    |  |  |  |  |

|                 |                      | 2.6.3                           | The FRIENDS System                                | 33 |  |  |  |  |

|                 |                      | 2.6.2                           | OpenC++                                           | 32 |  |  |  |  |

|                 |                      | 2.6.1                           | The Common Lisp Object System Metaobject Protocol | 31 |  |  |  |  |

### **Chapter 1**

## Introduction

Embedded systems are application-specific computer systems that are deployed as part of a larger machine. Unlike general-purpose computers they typically perform only a small set of tasks that cannot be changed. Also, they are often transparently integrated into their host systems so that the user is not aware of their presence. Embedded systems are used in many different domains. Consumer electronics is one of the commonest markets and they can found in common household items such as mobile phones, microwaves, televisions and digital watches. The automotive industry also makes extensive use of these systems to create engine management or system diagnostic modules. They are even used in high-integrity systems, such as aeroplanes, factories, medical devices and power stations. In general, almost all digital devices contain some kind of embedded computer system.

Due to their intended applications, embedded systems often have a larger set of design requirements than general-purpose computer systems. Their physical size limits many factors such as processing power or the amount of available memory, meaning that efficiency is very important. Similarly, embedded applications are often battery-powered so they must limit the amount of energy they consume. As they must interact with the outside world they are commonly subject to strict timing requirements, leading to many embedded systems being classified as *hard real-time* systems. [9] Designing such systems has always been a challenge, but it is becoming ever more difficult as embedded technology enters more aspects of daily life and systems become much larger and more complex.

Initially, the substantial cost associated with digital technology meant that computer systems would only be used in situations that actively required computer control and would be otherwise impossible if attempted by a human operator. One such example is precision engineering, where a human would be incapable of the fine motor skills required and so computer-controlled actuators are used. However as technology progressed and the cost of microprocessors decreased, embedded systems were integrated into more and more devices where computer control was not essential but instead simply added new features or improved existing ones. Televisions, washing machines, telephones and cars are all examples of this trend. As silicon technology advanced further, processors became so cheap that they are now commonly used to actually reduce the cost of a system. Often a large number of integrated processing elements can be replaced by a single embedded CPU with no loss in computational

#### 1. Introduction

power, thereby reducing the overall build cost of the system. Indeed, the pervasiveness of embedded systems is so great that of the nearly 8.3 billion microprocessing units shipped in the year 2000, 8.14 billion (98%) were used in embedded applications. [55]

Today, consumer expectation is increasing on a daily basis and the amount of functionality that is embodied by embedded systems is constantly growing. Embedded systems are required to become more powerful in order to meet these increasing demands whilst still maintaining their real-time properties to ensure that reliability and safety are not compromised. This makes the development of embedded hardware and software more difficult and error-prone, thereby increasing its cost and time-tomarket.

The problem examined by this dissertation is that this increase in design size and complexity has not been met by a corresponding increase in designer productivity. Apart from in a few specific domains, designers must still use low-level circuit description tools to manually create their systems. This is time-consuming, error-prone, and requires expertise and experience. In an attempt to mitigate these problems, high-level synthesis systems have been developed that allow hardware design to take place at a higher level of abstraction. Unfortunately, no current system is powerful enough to have been adopted by mainstream designers. Current synthesis techniques impose restrictions on the designer that do not scale when they are used to describe entire systems, resulting in implementations that are either inefficient or do not meet the non-functional constraints of the application. In this document, the problem is examined further and potential solution areas are examined.

### **Chapter 2**

### **Literature Review**

This section discusses the role of embedded systems and how they have developed over recent times, evolving into Systems-on-Chip (2.1.1) and Networks-on-Chip (2.1.2). It then discusses FPGAs (2.2) and a number of techniques that are associated with the use of them. The review then moves to concentrate on the ways in which we can describe hardware designs with a software program, looking at both Hardware Description Languages (2.3.1) and the hardware synthesis of high-level programming languages (2.3.3). It then briefly discusses the topic of hardware/software codesign (2.4) before moving on to metaprogramming techniques. The main techniques mentioned are reflection (2.5), metaobject protocols (2.6), and aspectoriented programming (2.7.1).

#### 2.1 Design of embedded systems

At the time when the first embedded systems were being developed, the available fabrication technologies meant that only relatively small circuits could be built. Most designs were presented in the form of a schematic diagram showing the circuit as a design composed of logic gates or transistors. Software was not a concern because something as complex as a microprocessor could not be manufactured in a way that was small or cheap enough for its inclusion to be considered. Designing with schematics was advantageous as it introduced no inefficiency and no further tools were required to convert the design to a useable format for implementation in actual hardware. However, the lack of abstraction meant that such schematic diagrams were very difficult to work with when design sizes began to increase.

Since the development of the integrated circuit in the early 1960s and consequently the microprocessor in around 1970, the logic density and effective computational power of digital circuits has increased massively. Fuelled by this, the power and complexity of embedded systems have increased similarly, and schematic-level design is now no longer a viable option for most designers as it is too cumbersome to work with. To remedy this, Hardware Description Languages (HDLs) were developed<sup>1</sup> that

<sup>&</sup>lt;sup>1</sup>In 1983 ABEL [1] was devised for targeting programmable logic devices but it was not until 1985 that Verilog, the first modern HDL, was developed. VHDL followed in 1987.

provide a higher level of abstraction and allow for large amounts of circuitry to be designed using source code similar to a traditional programming language. (HDLs are described more fully in section 2.3.1.)

#### 2.1.1 The System-on-Chip paradigm

Previously, electronic devices were constructed using processing elements that were each contained within their own separate integrated circuits (ICs). These ICs were packaged in ceramic chips and communicated with each other over the routing on a printed circuit board to which they were all mounted. However as the complexity of embedded systems has continued to increase, it is now common to see ICs that embody an entire system rather than a single component. Rather than implement a single function, the ICs can now contain multiple logic cores all working in parallel to solve a single goal with little external routing required. This has become known as the concept of System-on-Chip (SoC), where a single device contains a number of logical modules which interact to solve a given task. SoC architectures have arisen because as silicon chip fabrication becomes more sophisticated, the circuits that can be imprinted upon them are faster, smaller and cheaper than an equivalent printed circuit board design. ICs often use less power and therefore generate less heat than printed circuit boards [59] which can be advantageous for devices that are built to operate on battery power. Finally, a SoC can be easier to design than the equivalent PCB-based design as the designer does not have to consider track layout, off-chip propagation delay or other extra-logical characteristics.

A particular challenge that arises from the SoC paradigm concerns the method of communication between the individual IP cores that the system is comprised of. This is commonly achieved by implementing ad-hoc bus architectures or by routing lengthy interconnecting wires across the silicon die. Whilst sufficient for the early SoCs, such designs do not scale well because of their reliance on a globally synchronised clock. Such a clock is difficult to support in a large system because of propagation delay and routing requirements [3]. Bus-based systems can also require a large amount of power and generate a lot of heat as driving a signal onto a bus involves asserting a large number of (often rather lengthy) communication lines.

#### 2.1.2 From System-on-Chip to Network-on-Chip

To mitigate these problems, many newer SoC designs are moving away from buses and employing on-chip networks instead. As discussed by Benini and De Micheli [3]:

"The most likely synchronisation paradigm for future chips is 'globallyasynchronous locally synchronous' (GALS), with many different clocks. Global wires will span multiple clock domains, and synchronisation failures in communicating between different clock domains will be rare but unavoidable events."

This describes a micro-network in which different modules of the SoC each form a communicating node on the network. The crucial difference in the Network on Chip

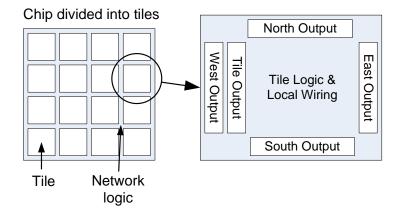

**Figure 2.1:** The Dally and Towles Network Architecture. The system is divided into a 2D grid of tiles with interconnection logic between the tiles to handle communication. [14]

(NoC) concept is that each node is a separate timing domain and data transfer between nodes is performed asynchronously. The presence of multiple clock signals affords designers a great deal of freedom and allows a number of the previously mentioned limitations to be overcome. Primarily, the use of a network reduces the problem of propagation delays between modules in the system by removing dependence on a global clock.

Also, as different sections of the SoC can be driven by different clocks, the critical timing paths of one section do not affect the paths of any other. This allows for parts of the system to be clocked at a very high rate, even if there are some sections that must be clocked slowly. Conversely, sections that do not require a high clock speed can be driven slower to use less power and generate less heat. Most NoC designs are based on a tiles, and one of the first such architectures can be seen in figure 2.1.

Tile-based networks are often proposed for NoC implementations because, as noted by Dally and Towles [14], unlike standard shared-medium networks such as Ethernet the available bandwidth of the network actually increases with the number of connected nodes. They are also more amenable to techniques that add fault-tolerance or adaptive load balancing due to the large number of available routes between sender and receiver.

Current work in the NoC field is still primarily concerned with exploring potential architectures or protocols that are likely to be of use in this emerging design paradigm. Zeferino and Susin [68] present a parametric architecture that can be adapted depending on the required network performance or available implementation area. More powerful networks require a larger amount of interconnect and logic to implement but they can support applications with higher bandwidth requirements. Wiklund and Liu [58] proposes an architecture that is designed to support hard real-time systems with strict bandwidth requirements. Rather than use a best-effort protocol to transmit a packet as soon as possible, as in Ethernet, their proposed network establishes virtual circuits based on an offline schedule to ensure communications will complete before deadline. Kumar et al. [40] concentrate more on protocol development and adapt the OSI model to create a four level communications stack that aids higher-

level development. Pande et al. [49] considers the design of a network switch that is particularly suited to NoC-style networks. They use wormhole routing in their network and produce a design that is expected to consume approximately 2% of a large NoC-based design.

The main weakness in much of the above work is that it is difficult to evaluate their effectiveness in real-world situations, so theoretical examples are used instead. As NoC is only just beginning to emerge as a valid design style, there are few existing systems that are suitable for use as case studies or comparisons. As more and more commercial systems are developed that use on-chip networks and the research field matures, it will become clearer what the actual requirements of a commercial NoC are and so therefore which NoC strategies show the most promise.

#### 2.2 Field-Programmable Gate Arrays (FPGAs)

An FPGA is an example of a class of programmable logic devices known as gate arrays. In a gate array architecture, transistors, logic gates, and other active devices are placed in a regular lattice pattern and connected with interconnect wires. These wires are configurable and can be arranged to connect the resources of the device in a structured manner. By placing the interconnect lines correctly, a process known as routing, the components on the device can be connected to form almost any desired circuit.

FPGAs were initially developed in 1984 by Xilinx and were marketed as an alternative way of evaluating ASIC designs. Previously, evaluating a designed circuit required that either the design was manually built from connecting discrete components, or it was fabricated as a custom-built ASIC. Both methods were time consuming and very costly. FPGAs changed this by giving the designer an implementation fabric onto which designs could be programmed. Evaluation could begin almost immediately, and once errors were found and corrected the device could be reused. This prototyping method drastically increased the efficiency of ASIC design, but also opened up new possible implementation methods. As the size and speed of FPGAs increased and their unit costs decreased, more and more embedded systems were developed that included an FPGA in the final circuit design, rather than an ASIC. This avoided the heavy set-up costs associated with creating a custom IC and is very suitable for products that are sold in low to medium volumes.

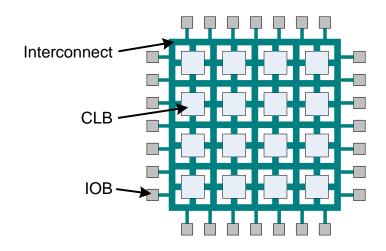

On a basic FPGA, the primary resources are Configurable Logic Blocks (CLBs), interconnect and input/output blocks (IOBs). (See figure 2.2) CLBs make up the majority of the components on the FPGA<sup>2</sup> and are used to create sections of logic that implement the primary functionality of the device. They are constructed from Look-Up Tables (LUTs) and flip-flops and can be programmed to perform one of a large set of logical functions on their inputs. CLBs are connected to each other by programmable interconnect which can be configured to selectively route signals across the FPGAs. In all modern FPGA architectures interconnect follows a hierarchical model. The majority of interconnect is named 'local interconnect' and is constructed from short wires that may only span a small number of CLBs. This is most commonly

<sup>&</sup>lt;sup>2</sup>It is the vast amount of interconnect that actually consumes the majority of the silicon area of an FPGA [7]

**Figure 2.2:** Simplified FPGA architecture showing CLBs surrounded by interconnect and interacting with the outside world though IOBs

used to connect the inputs and outputs of adjacent CLBs to form a single large logic function, such as a multiplier or shift register. In order to connect distant parts of the FPGA, 'global interconnect' exists which is comprised of longer wires that may span the entire width of the FPGA. Due to area constraints, global interconnect is much less common than local interconnect and so can often be a very limited resource. Finally, global clock nets are a special type of global interconnect which exist solely to propagate clock signals throughout the FPGA. Due to the complex hardware involved in reducing clock skew, there are generally only a few clock nets available on a device, 4 on the Xilinx Spartan-IIe [64].

#### 2.2.1 Advanced FPGA architectures

Whilst all FPGAs are comprised of LUTs and interconnect, modern FPGAs contain a number of additional embedded modules for performing specialised tasks. These allow for greater design flexibility as they operate at a high speed and can be used to implement functions that would take up a great deal of the normal FPGA fabric. These modules are often connected via switching blocks to the global interconnect lines and can therefore be driven by any other part of the FPGA. Some of the more common additional modules are described here.

For performing complex control operations or processing large amounts of data, many high-end FPGAs include processor cores as part of their architecture. For example, the Xilinx Virtex-4 [65] contains four PowerPC 405 cores. These cores operate independently of each other and can be driven from different clock signals if required. The surrounding logic presents the cores with information and collects the results once processing is complete. Due to the fact that these cores are implemented as embedded ASICs rather than derived from the normal FPGA fabric, they can be clocked at much higher rates than most FPGA-based processor implementations.

Most applications require some form of memory to store programs or data. Whilst

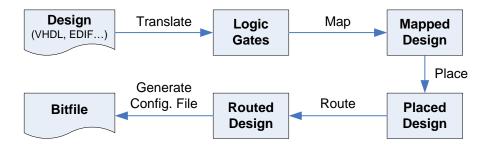

Figure 2.3: The standard FPGA design flow.

RAM can be synthesised by combining LUTs appropriately, this is a very inefficient use of resources. As a result, distributed RAM is a common feature in modern FP-GAs. In Xilinx FPGAs, the distributed RAM modules are called BlockRAMs and on the largest Vertex-5 FPGA [66] there is over 11 megabytes of storage available to the designer. Different FPGA families have different RAM layouts, with some favouring a large number of smaller RAMs and others concentrating most of their memory in a few large RAM banks. The initial contents of Xilinx BlockRAMs can be set from the configuration bitstream when the device is programmed and each BlockRAM can be arranged to have different widths and depths. For example it could be accessed as *n* different 16-bit values, or 2*n* different 8-bit values. All Xilinx BlockRAMs are dual-ported, allowing for two processes to access the RAM simultaneously, but this is not the case for all FPGAs. The memory blocks on high-end Altera FPGAs can be configured to operate in single-port mode, or to relinquish some storage capacity to add extra access ports as required by the application.

In addition to embedded softcores and distributed RAM, many other design elements are being integrated into FPGA fabrics. Some devices include dedicated multiplier units that can perform calculations much faster than similar logic synthesised from the CLBs, clock management circuits distributed across the FPGA help to manage clock skew and create stable clock dividers and high-speed I/O modules such as the Xilinx Rocketl/O modules allow off-chip communication at 11 Gbit per second. The use of these special design elements is normally controlled by the vendor's synthesis tools which attempt to infer when one of them may be of use to a design. For example if the synthesis tools create a large enough multiplier, it may choose to use an on-chip one rather than synthesise one directly from CLBs. However for many design elements such inference cannot be used and elements like Rocketl/O transceivers or embedded processing cores must be manually instantiated using a hardware description language like VHDL.

#### 2.2.2 The FPGA design process

FPGAs store their current configuration in specially reserved configuration memory. As this memory is volatile, the device must be reconfigured each time it is powered up. In the situations when the device has not been loaded with a set of configuration data, known as a bitfile, all user-accessible pins default to a high impedance state and the device remains idle. The process of creating a bitfile to program an FPGA with is described here and shown in figure 2.3.

- Design The required design is expressed in a form that is acceptable to the FPGA design tools. This may be a schematic, an EDIF netlist, source code written in a hardware description language (section 2.3.1), or source code written in a higher-level language that can, though the process of synthesis, be converted to a hardware description language (section 2.3.1).

- Translate The user input is translated to logic gates, essentially converting all forms of input to the schematic form.

- Map The resulting logic gates are mapped into CLBs and other atomic elements of the target FPGA fabric.

- Implement The design is implemented on the target FPGA. This stage, consists of two main operations:

- **Place** The mapped CLBs are placed onto the device. This is the first point at which a design can be determined to be too large for the target FPGA. The mapping algorithm will attempt to keep logically related CLBs together to minimise routing. The placement algorithm is a version of the bin packing problem and is NP-complete. [67] As a result this stage can take a long time to execute and at times of high utilisation the placer must resort to a simple exhaustive search.

- Route The interconnect between the placed CLBs is finalised. The routing algorithm attempts to use the shortest interconnection lines possible to reduce propagation delay and power consumption. Due to the large amount of interconnection required by most designs, it is possible for a design to fit onto a device at the placement stage but for routing to be impossible due to lack of space. Again, this problem is NP-complete.

- 5. **Bitfile creation** The placed and routed design is converted to a bitfile that can be used to configure the target FPGA. The final bitfile can only be applied to the exact FPGA model for which it was created, even different FPGAs from the same family cannot share bitfiles.

Once this process is complete, the FPGA can be configured by loading the created bitfile into its configuration memory. Different FPGAs provide different programming interfaces but all modern FPGAs implement at least two main modes, a serial interface and a JTAG interface.

The serial programming interface is simple and is used to program the device from an attached memory chip very quickly. As previously mentioned, FPGA configuration memory is volatile and so the device must be reconfigured every time it is powered. As a result, if an FPGA is used in a complete system the configuration bitfile must be stored in some form of non-volatile memory, such as a PROM. The PROM can be connected to the FPGA via the serial interface and configured to transfer the stored bitfile to the FPGA very quickly. Most FPGAs, including the Xilinx Spartan and Virtex series, can automatically drive a connected memory chip to retrieve the configuration bitfile without additional logic. Whereas the serial interface only allows for bitfile transfer, the JTAG port [31] is a much more complex interface that can also be used for readback and debugging. JTAG is standardised as IEEE 1149.1 and is used in many embedded systems to assist with debugging and maintenance throughout the design and lifespan of the system.

#### 2.2.3 Partial Dynamic Reconfiguration

A major benefit of an FPGA-based implementation fabric is the ability to reconfigure the device at runtime. Most systems that include an FPGA component simply configure it once when power is first supplied and the running design remains the same until the power is removed and the device shuts down. However, the configuration engines of modern FPGAs are much more flexible than this and they allow a running device to be stopped and reconfigured with a different bitfile, effective turning it into a different circuit that implements a different set of functionality. This gives rise to entirely new application areas and allows for an FPGA design which can respond to a mode change or other significant event in the system by changing its behaviour drastically. Effectively, this dynamic reconfiguration allows for a number of mutually exclusive features to be implemented on the same hardware at different times, thereby reducing silicon area and power consumption.

A good example application of this ability is a video decoder system that supports many different video formats. The system implements its decoding functions in hard-ware as this is much faster than a software-based solution. However, a dedicated ASIC is required to decode each different video format that it supports. If an FPGA is used instead, then different configurations for the various formats can be stored in a single ROM chip and then programmed in just before decoding commences. This allows for the system to display the speed of a hardware-based implementation but to support many different formats without dedicated hardware for each one. Also, firmware updates can be issued to add support for new formats after the device has been shipped.

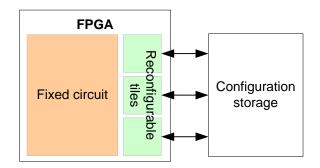

Recent FPGAs also allow for a more fine-grained reconfiguration mechanism. Rather than reconfiguring the entire device as described above, it is possible to load a partial bitfile which only affects a subset of the device whilst the unaffected areas continue to run. This technique is known as *partial* dynamic reconfiguration <sup>3</sup> (PDR) and was introduced in the mid 1990s with the Xilinx 6200 FPGA[13]. Not all FPGAs support PDR and those that do display differing capabilities depending on their architecture. For example, the Xilinx Virtex-II must be reconfigured in whole columns whereas the Virtex-4 relaxes this constraint and allows for individual tiles from a grid to be independently reconfigured.

#### 2.2.4 Applications of Partial Dynamic Reconfiguration

PDR has many theoretical uses that are related to the concept of 'virtual hardware'. By analogy to the concept of virtual memory, physical hardware could be made to appear larger than it actually is by swapping circuitry in and out of the FPGA from dynamic memory or magnetic storage (see figure 2.4). When a new feature is required by the system it is swapped in to the FPGA using PDR and activated. Later, when it is no longer needed it can be removed to free up space and reduce power consumption. Both of these operations need not affect the rest of the system and the parts of the FPGA that are unaffected by the reconfiguration remain active at all times.

<sup>&</sup>lt;sup>3</sup>Different authors tend to use slightly different terms when describing this concept; other common terms are 'partial reconfiguration' and 'active partial reconfiguration'. This document will use 'partial dynamic reconfiguration', or PDR.

**Figure 2.4:** Illustration of partial dynamic reconfiguration. Self-contained tiles of the design can be swapped between the FPGA and external storage in the same way that conventional virtual memory swaps pages of data between main memory and magnetic storage.

Although PDR is still emerging as a design technique, numerous research projects have begun to exploit its potential in the field of reconfigurable computing. A common paradigm that PDR is applied to is that of a custom instruction set processor. Such a processor will generally provide a basic instruction set that is fixed but not very expressive and then the system designer can create new instructions that are dynamically loaded into the CPU when their opcodes are encountered at runtime. A classic example is the Dynamic Instruction Set Computer (DISC) [60]. DISC is entirely implemented on a standard FPGA, using a portion of the device as a fixed execution controller and the rest of the device as space in which to store custom instructions. Analysis of DISC shows that whilst the speed up obtained when performing general-purpose computing tasks is modest, application-specific tasks can be accelerated by up to 24 times by carefully selecting custom instructions that would be heavily used by the target application.

The Chimaera reconfigurable processor [28] is more of a hybrid approach. Chimaera is an ASIC-based CPU which contains an amount of embedded FPGA-style reconfigurable hardware. Chimaera uses this reconfigurable hardware to store the execution units of custom machine instructions, whilst the ASIC section performs all standard operations. Hauck et al. claim speed ups of up to 160 times in their system, but in reality such impressive results can only obtained in rather artificial circumstances with carefully hand-mapped examples. The authors state that general-purpose computing can be shown to be accelerated by approximately a factor of 2, but this is mitigated by the inevitable slowdown that is observed when moving from an entirely ASIC processor to an FPGA-based design. PDR has also been used to create a reconfigurable co-processor that sits alongside a standard CPU [29].

Marescaux et al. [43] and Huebner et al. [30] both propose NoC-based designs that may allow PDR to be used in a more general sense than the systems above. When an FPGA is partially reconfigured, care must be taken to maintain routing amongst all parts of the device that are still active. If an interconnection route passes through an area that is reconfigured then the connection will be broken. Reconfigurable processors avoid this by constraining the type and size of designs that can be swapped into the FPGA, whereas these network-based systems proposed attempt to relax this constraint and allow for general-purpose hardware to be swapped as required.

Currently, PDR is only employed in academic situations and has not been adopted

for commercial or industrial systems due to a number of reasons. Primarily, because the concept is still relatively recent there is only limited tool support for PDR. Xilinx's PlanAhead hierarchical design tool attempts to simplify PDR but it is still considerably more difficult to use than a standard static design. As a result many designers will be discouraged from using what can be viewed as experimental technology. Also, a system that uses PDR can be difficult to verify from a safety-critical point of view due to the fact that during reconfiguration the device exists in an unknown state. After completion, extreme care must be taken to avoid metastability and other undesirable effects. Despite its potential benefits, it is unlikely that PDR will become a mainstream implementation choice until tool support has matured and at least some of these problems can be handled automatically.

#### 2.3 Describing hardware with software

#### 2.3.1 Hardware description languages (HDLs)

As mentioned in section 2.1, as the size and density of digital circuits develops it becomes increasingly impractical to describe them using schematic diagrams alone. The gate count of modern processors is measured in the tens of millions and a complete schematic diagram would be unmanageably large. Also, the poor level of abstraction afforded by schematics makes working with such diagrams difficult and error prone. To counter these problems, hardware description languages (HDLs) were developed. HDLs are a software-based technique for describing the arrangement of elements in a digital circuit. They describe the circuit's operation and organisation and frequently they can be used to simulate the described circuit and thereby verify its design. HDLs are a higher level of abstraction than schematics as they include notions of time and parallelisation. HDLs that express nothing more than the connections between circuit elements are called netlist languages, the most common example of which is EDIF [18]. Netlist languages are often used for storing schematics in a digital format and are notionally equivalent in terms of abstraction and complexity.

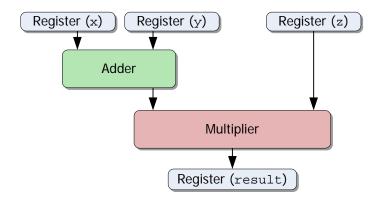

HDLs are implemented as standard textual languages that resemble software source code. A tool called a synthesiser is used to transform the HDL design into a netlist that can then be implemented as an ASIC or on an FPGA. This process is similar to compilation of standard source code and undergoes many similar steps, such as syntax checking, tokenisation and the generation of an abstract syntax tree. HDLs are easier to work with than schematics as they allow the designer to express relatively complex concepts that can be automatically translated to actual hardware by the synthesis tools. For example, the statement:

result <= (x + y) \* z;

will automatically synthesise an adder and a multiplier of the correct widths and connect them as shown in figure 2.5.

The two most common HDLs that are in use today are VHDL [11] and Verilog [16]. They both provide a rich expressive environment for designing digital circuits and are widely supported by industry-level toolsets. VHDL (VHSIC Hardware Description

Figure 2.5: Pseudo-schematic showing the result of synthesising result <= (x + y) \* z;.

Language) was initially developed as a way of documenting the behaviour of ASICs, but has now grown into a tool for designing, simulating and synthesising them also. As a result only a subset of VHDL can be directly synthesised to hardware, the rest of the language can only be simulated. VHDL was designed to be similar in style to the Ada programming language [2] and so it shares a very similar syntax, is case insensitive and is strongly-typed. Verilog, in contrast, was designed to be familiar to C programmers so it is case sensitive and uses a preprocessor. As with VHDL, only a subset of Verilog is synthesisable.

Both languages differ fundamentally from their procedural language counterparts, however. Ada and C are both imperative languages whereas VHDL and Verilog are declarative. This means that whilst in a standard programming language two consecutive statements are executed one after the other, in a HDL they are generally executed in parallel. This is because each statement describes a hardware element that is operational at all times. The designer must implement state machines and other techniques in order to achieve sequential execution.

Both languages offer support for structured system-level design because a designer can describe a component using high-level parts of the language that are outside their synthesisable subset. Whilst this code cannot be automatically synthesised to hardware, it can be simulated and and verified so the designer can be sure that the behaviour of the component is correct before attempting to express it as synthesisable code.

#### 2.3.2 SystemC

A hardware-oriented language that is very well supported by industry today is SystemC. An IEEE standard, SystemC [32] is a system description language that can be used to design and simulate systems at multiple levels of abstraction. It is based on  $C_{++}$  [21] and implemented as a large library of classes and macros, thereby keeping the same syntax as  $C_{++}$ . It can be viewed as both a hardware description language and a simulation language, as whilst its main aim is to verify the design of a system, a subset of the language can be synthesised directly to hardware. However, Grimpe and Oppenheimer [26] notes that the synthesisable subset of SystemC is equivalent

in terms of expressive power to that of VHDL or Verilog, so it does not offer an extra layer of abstraction in the final hardware description.

SystemC models concurrent processes as 'modules' and describes the communications between them using a library of built-in primitives or user-defined composite types. System composition is modelled by 'ports', which are the connection points between which modules can exchange data. Transaction-level modelling can be used to describe these interactions between system components at a high-level of abstraction, and so simulation of the modelled system is often much faster and more comprehensible than VHDL or Verilog. Finally, one of the main strengths of SystemC is that it allows the designer to describe a system in very high-level abstract terms and verify it quickly through simulation. Then, in order to implement the design in actual hardware, individual components can be elaborated and a reification for each one created independently. Whilst this design style is also possible in VHDL and Verilog, SystemC provides more advanced modelling constructs and simulation is much more efficient.

Most of the criticisms of SystemC are related to its base language, C++. As C++ is a sequential language, describing concurrency and timing properties requires the use of preprocessor macros and library calls that can seem counter-intuitive, whereas in other HDLs these constructs are first-class parts of the language. This can be seen in figure 2.6, a SystemC description of a NAND gate. Many preprocessor macros are used (SC\_MODULE, SC\_CTOR...) in order to implement syntax that is not available in normal C++. Also, due to fact that SystemC is attempting to make C++ appear to be a declarative like VHDL or Verilog, it can be difficult to separate code that actually describes hardware from code that exists solely to aid the simulator. Figure 2.7 shows an equivalent VHDL description for comparison.

Also, as noted by Edwards [17] it is quite easy to inadvertently develop a nondeterministic SystemC model due to the fact that the simulator must mimic true concurrency on a sequential processor. This leads to a slightly different execution order each time the simulation is run, and so race conditions can develop when global variables or shared resources are used. This can be difficult to detect from the simulator without extensive testing and so the bug will only be discovered when the system is fully implemented in hardware.

#### 2.3.3 High-level language synthesis

Whilst hardware description languages greatly aid the design of embedded hardware, newer design trends are beginning to strain current techniques. With the move to architectures based on the Network-on-Chip (section 2.1.2) paradigm and the increasing size of modern embedded systems, the current level of abstraction afforded by HDLs such as VHDL and Verilog is starting to prove insufficient. Current HDLs force the designer to express the functionality of their system in terms of state machines and interacting parallel processes. This works well for low-level modules that must interact with other off-chip device, but for larger modules and for general system-level behaviour it can become difficult and is a barrier to code maintainability and reuse.

As a result, there has been a great deal of research into the field of high-level language synthesis. The aim of such research is to increase the abstraction level of

```

#include "systemc.h"

SC_MODULE(nand2) // declare nand2 sc_module

{

sc_in<bool> A, B; // input signal ports

sc_out<bool> X; // output signal ports

void the_nand2() // a C++ function

{

X.write( !(A.read() && B.read()) );

}

SC_CTOR(nand2) // constructor for nand2

{

SC_METHOD(the_nand2); // register do_nand2 with kernel

sensitive << A << B; // sensitivity list

}

};</pre>

```

Figure 2.6: A SystemC specification of a two-input NAND gate.

```

use ieee.std_logic_1164.all;

entity nand2 is port

(

a,b: in std_ulogic;

x: out std_ulogic

);

end nand2;

architecture struct of nand2 is

begin

process (a,b)

begin

x <= a nand b;

end process;

```

end struct;

Figure 2.7: A VHDL specification of a two-input NAND gate.

synthesisable HDL code, thereby making it simpler for the designer to create large systems without having to consider low-level implementation issues. Such high-level languages attempt to provide more expressive power than is afforded to the designer by standard HDLs. For example, this may include support for object orientation, transaction modelling or automatic generation of state machines. There are a number of high-level languages that can be synthesised to hardware, this section will detail some of the more commonly seen examples.

#### 2.3.4 Handel-C

Handel-C [6] is a programming language developed by Celoxica for rapid prototyping of hardware designs to FPGAs and ASICs. It is implemented as a subset of ANSI C with a number of extensions that allow for parallelism and communication between parallel blocks. Due to Handel-C's stated goal of rapid prototyping, it does not allow the designer as much control over the implementation strategy as standard HDLs. Instead, it allows for more abstract concepts to be defined in code that looks very similar to standard sequential C. All state machine and control flow hardware is inferred and generated automatically by the Handel-C synthesiser. This means that an off-the-shelf solution that is written in ANSI C can often be synthesised directly to hardware, after minor rewriting for the conversion to Handel-C.

The process of synthesising Handel-C to hardware is very similar to the way in which normal C is compiled to object code. The compilation strategy is basically recursive descent, but rather than recursively generating machine code the synthesiser generates small hardware blocks which are recursively connected together. The resulting circuit is expressed in the EDIF format which can then be optimised by any number of tools before the design is converted to an FPGA bitfile by vendor-specific toolchains.

The Handel-C design process is fundamentally different to the way in which a circuit is built up with a hardware description language such as VHDL. As mentioned previously, VHDL is a declarative language whereas Handel-C (like its parent language C) is imperative. As a result, to describe two events that occur sequentially can be difficult in VHDL as a one-hot state machine must be described that switches between the two events in the correct order.

```

process Do_The_Tasks(clk, current_state)

begin

if (clk'event and clk = '1') then

if (current_state = 1) then

Do_Task_One;

elsif (current_state = 2) then

Do_Task_Two;

end if;

end if:

end process;

process Change_State(clk)

begin

if (clk'event and clk = '1') then

if(current_state = 1 and Task_One_Finished) then

current_state <= 2;</pre>

end if;

```

end process;

In Handel-C this is much simpler because state machines are automatically inferred by the synthesiser and the inherently sequential nature of C can be exploited by simply calling the two items one after the other.

```

void main(void)

{

Do_Task_One;

Do_Task_Two;

}

```

Like most standard programming languages, normal Handel-C designs can only include a single clock source. The reason for this is that Handel-C was designed to have a very predictable timing model and the provision of multiple clock sources would undermine this aim. It is possible to make use of multiple clock sources in a Handel-C project but this is achieved by creating multiple designs, each with its own void main (void) function, and then linking them together using the Handel-C IDE. The designs can then export and import communication channels to share data asynchronously. This approach is quite limited because the encapsulation of design units is performed outside of the language and it gives no scope for modular composition, meaning that designs cannot be nested. Also, only channels can be shared between designs; variables, signals, interfaces and functions cannot.

There are a number of problems with Handel-C that limit its potential for exclusive use in the embedded systems market. First, as previously mentioned Handel-C has a very simple timing model that is intended to produce circuits with easily predictable performance characteristics. Essentially, the model states that "every assignment and communications statement takes one clock cycle, everything else has no cost". [57] This means that all assignments will take the same amount of time and so it is possible to inadvertently reduce the maximum speed of the entire circuit by introducing a single statement with a large propagation delay. This is illustrated in the following example:

```

void assignments(void)

{

x = a + b;

y = a >> 3;

z = (a * (b + c)) / (d * e);

}

```

In this example, all three assignments take exactly one clock cycle. However, the assignment to z describes a large circuit with a significant propagation delay. If this is the longest path in the circuit then the maximum clock rate of the entire design is reduced. To avoid this, the programmer must manually split the assignment into multiple stages. This splitting cannot be done by the compiler as it would change the semantics of the program, and a statement that originally took one clock cycle would take longer.

Related to this problem is the fact that even though Handel-C appears to be standard C, it is in fact targeted at a very different implementation. Consequentially, a programmer who forgets this and writes in the style that they would for normal C will end up with an inefficient design. This can be seen when comparing loop termination constraints in the two languages. In C it is common to compose a loop as

such: for (x=0; x<10; x++). However it is more efficient in Handel-C to replace the less-than comparator with an inequality check: for (x=0; x!=10; x++). The inequality check is a simpler circuit than the comparator that is required by the less-than operator and so it results in a smaller design. Finally, due to its reliance on standard C, Handel-C lacks real modular decomposition or encapsulation making it difficult to use when producing larger designs and limiting the language's potential for code reuse.

#### 2.3.5 Other synthesised languages

Aside from those already presented there are a number of other languages that are targeted at hardware rather than at object code, but few have reached the level of commercial acceptance that Handel-C has attained.

The York Hardware Ada Compiler (YHAC) [57] has shown success in retargeting the Ada language to generate hardware designs in the form of EDIF netlists. (Ada is a very large language so only the Ravenscar subset [8] is implemented.) YHAC translates sequential Ada into hardware by generating one-hot state machines for each procedure. Unlike Handel-C, these state machines allow for individual operations to take multiple clock cycles, thereby reducing propagation delay in the final design and maximising potential clock speed. However, the inefficiency of a one-hot implementation style means that circuit scalability can be reduced and sizable programs can often be translated into very large circuits. YHAC can make use of Ada's native support for concurrency and will create a new state machine for each task, giving the programmer access to true parallelism. Therefore, YHAC implements Ada's coarse-grained concurrency model instead of the fine-grained model found in Handel-C.

Work by Cardoso and Neto [10] attempted to translate Java bytecodes into a dedicated hardware circuit that can be implemented on runtime reconfigurable hardware. The technique uses temporal partitioning, which separates bytecodes into graphs that do not need to occupy the device at the same time. Then, the system attempts to generate separate circuits for each temporal partition that then can be executed by a reconfigurable framework which implements the virtual hardware paradigm (discussed in [41] and [25]). The system extracts control dependency graphs, data dependency graphs and data flow graphs from the bytecodes and uses them to create the partitions. Problems with this approach are centred around its use of Java bytecodes as an input source. The translation of sequential byte codes to hardware can be rather inefficient as it results in circuits that are influenced more by the design of the Java virtual machine than by the source code from which they were generated. For example, the work does not make reference to custom datatypes, a one of Handel-C's strongest features. In Handel-C, if an integer will only ever take 4 values it is possible to implement it with only 4 bits rather than the default 16. This results in significantly reduced circuit size because all calculation units that operate on this variable need only be a quarter of the width. With the byte code approach, there is no way to carry this bit width information from the programmer to the compiler and so default implementation widths must be assumed.

Lava [4] takes a different approach to the languages above by using the Haskell functional language to describe circuits rather than an imperative language like C or Ada. Functional programming is based on the notion of computation as a series of function evaluations with little or no persistent state, as opposed to imperative languages that rely on a global state that is affected by procedures and subroutines. It is argued that functional programming is a better paradigm to describe hardware that performs digital signal processing due to the lack of state information in such designs. Lava works by embedding VHDL-style code in low-order functions and building a type system on top of this to ensure consistency. Higher-order functions can then be used to succinctly describe regularity that would ordinarily involve repetitive VHDL code (such as when describing look-up-tables, or densely-connected networks). As a result, Lava is very well suited for defining both the structure of a design and the way in which it is composed from smaller sections.

Lava allows for functions to have different interpretations, where only one of these creates an actual netlist. Other interpretations instead allow for designs to be simulated and verified. As Lava is a functional language, it is best used for describing circuits that could be considered pure functions, such as arithmetic operators or fourier transforms. As a result, Lava is not as much a general-purpose HDL as it is a domain-specific one. The scalability of such a system to support large designs is unclear as Lava's supporting literature states that the largest circuit it has been used to describe is a 128-bit wide combinatorial multiplier.

#### 2.3.6 Summary

In summary there is currently no hardware-targeted language that that does not imply rather severe restrictions on the type of system that it can build efficiently. For example, Handel-C is good at creating circuits that are described by its one-hot state machine implementation strategy, but for designs that are best implemented using mainly asynchronous logic it can only describe an inefficient solution that is unnecessarily large and takes longer to execute than required. Similarly, Lava is based on a function composition paradigm that describes signal processing circuits well but cannot express state easily. This is a common problem with synthesis systems as they can only create circuitry using a single implementation strategy and, outside of a few pragmas, there is no language that allows the designer to override this to better suit their current project.

Unlike high-level synthesis, Hardware Description Languages give the designer the power to create almost any circuit that they require, but not without committing considerable effort to both development and verification. The end result is that high-level synthesis is desired for its speed and power when compared with HDLs, but it often cannot be used because it does not allow the designer enough control over the generated hardware. Instead, a hybrid solution may be employed. For example, high-level synthesis can be used to design the main processing cores of a circuit but their communications infrastructure may be described with an HDL such as Verilog.

It appears that high-level synthesis has hit a self-imposed limit and it will not improve without a change in the way it is realised. As mentioned above, synthesis works well within a narrow design space, but rapidly diverges from the optimal solution outside of this space, to the point where often large classes of designs cannot be implemented at all. A reason for this is that it is impossible to automatically synthesise a design artifact that cannot be directly expressed by the source language. For example, C is a single-threaded language with no concept of parallelisation or inter-task

**Figure 2.8:** A common problem with undirected place and route. The last two wires of the CPU-memory bus are routed around a third component, resulting in a mismatched bus.

communication. As a result, Handel-C can only synthesise circuits that make use of these concepts through its extensions to C that enrich its original semantics.

These language extensions may be tempting, but they cannot completely bridge the semantic gap between design space and implementation fabric because both are changing at a pace that is far more rapid than that of the language. For example, the globally-asynchronous, locally-synchronous design paradigm was not of wide commercial interest ten years ago but is now recognised as an important new direction. As a result, new classes of hardware designs are required that are poorly covered by languages like Handel-C. Also, these designs may be implemented on currently unseen hardware because FPGAs are constantly developing with the introduction of new embedded cores or different communication methods. Extensibility of synthesis-based languages is therefore something that requires further investigation.

Finally, a problem common to both high-level synthesis languages and HDLs is that they rarely allow the actual physical layout of the design to be specified. They concentrate on describing functionality and a separate place and route tool is used to determine the actual physical location of the constituent circuit elements. The designer does not control this and the placer does not have access to any high-level structural information, only a netlist that is output from the synthesis tool. Often this is sufficient, but there are some situations when the designer needs to influence placing decisions. For example, it is often desirable to keep all wires of a bus running approximately parallel so they are of similar length and therefore display a similar propagation delay. If bus wires are mismatched then signal synchronisation issues can arise leading to data transmission errors. However, as most place and route tools do not have access to structural information, it can be hard to infer that a certain eight signals comprise a bus and should therefore be routed together. Instead the wires are routed individually and this can lead to the situation shown in figure 2.8.

#### 2.4 Hardware/software codesign

Hardware/software codesign is an active field of research which is primarily motivated by the observation that, for most embedded systems, much of their functionality can be either implemented as dedicated hardware or as a software routine running

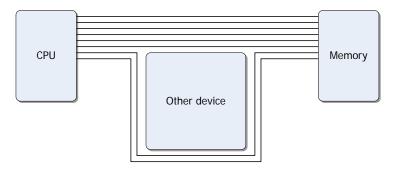

Figure 2.9: The target architecture of classical hardware / software codesign

on an embedded microcontroller. Both approaches carry inherent advantages and disadvantages and codesign attempts to balance these to find a sufficient design that meets restrictions placed on various metrics such as execution time, hardware density, power consumption or build cost.

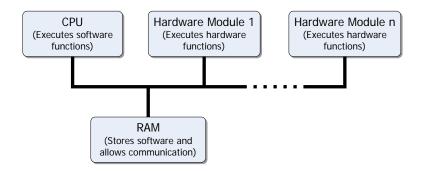

In the classic description of codesign [61], the operation of a system is specified in an implementation-independent way along with a quantitative list of requirements that the final implementation must meet. The codesign engine then creates the hardware / software partition by assigning the various functions of the system to either hardware or software. The hardware functions are synthesised to dedicated hardware and the software functions are compiled to opcodes for execution on a predetermined processor core. Once these processes are complete, the entire system can be evaluated by a cosimulation engine that returns a set of performance metrics. If these metrics show that the system does not meet its specification the process is repeated. This time, however, the hardware / software partition is moved and so the implementation method for some functions is changed. This new implementation can then be regenerated and reevaluated until a solution is found that meets the system's initial constraints.

The target architecture for such classical codesign systems involves a single shared system bus, upon which sits a single CPU (to execute the software tasks), a number of custom hardware co-processors (to implement the hardware tasks) and a block of shared memory (see figure 2.9). More recent work has reduced this restriction; for example work by Niemann and Marwedel [47] describes a system that supports multi-processor architectures and Kalavade and Lee [33] examines the partitioning problem when applied to more general architectures.

Due to the lack of a truly implementation-independent language for expressing a system's functionality, all codesign frameworks must be either software-based, or hardware-based, depending upon the format in which the design is initially specified. In a system such as Cosyma [22], the entire design is described in a specially-created superset of C called  $C^X$ .  $C^X$  is still a software language, it simply augments C with a few necessary concepts, such as that of tasking. Therefore, initially a Cosyma design is entirely implemented in software. When the system is run, it uses a specified cost function to evaluate the design and then begins to automatically move parts of the code into dedicated hardware through the use of a synthesis engine. It uses the simulated annealing algorithm to search for a partition that meets the design requirements.

Conversely, the work by Gupta and De Micheli [27] is hardware-based because the initial system specification is a circuit design written in the language HardwareC. HardwareC, as its name implies, adopts most of the semantics and syntax of C but is modified to allow unambiguous hardware modelling. It resembles VHDL in part as it is a declarative language based on *processes* and *blocks* and it handles concurrency natively. In this work, only when the system cannot meet its stated requirements are sections of hardware moved to the software partition. This is achieved by translating from HardwareC to standard C using a code generation engine and then compiling the new code for a generic microprocessor. Despite their differing approaches, both Cosyma and the work by Gupta and De Micheli achieve similar levels of overall success, with acceleration factors ranging from no difference up to approximately twice as fast depending on the specific application.

#### 2.4.1 Problems with codesign

There are a number of barriers to progress in the codesign field, but perhaps the most pressing is that the task of searching all possible partitions for an optimal solution is intractable and requires an exhaustive brute-force search in the general case. Codesign can be considered to be a search problem and so Wolpert's "No Free Lunch" theorem [62, 63] can be used to state that the problem of codesign can never be simply 'solved' in the general case. There is no single search algorithm that will be able to perform better than an exhaustive search of all possible partitions for every possible problem. As a result, heuristic-based search algorithms must be used and it is this that has been the focus of much recent work. [19, 20, 34, 56] It should be noted that this problem can be slightly mitigated in practice, as the *optimal* solution is rarely required, merely one that is good enough to meet the system requirements.

Secondly, most codesign frameworks rely on an accurate measurement of the performance metrics of the partitioned design to guide their heuristic search. In other words, the system makes decisions commonly based on the worse-case execution time (WCET) of both code and hardware and the expected size of compiled code and synthesised hardware. There is a massive body of work concerned with calculating the WCET of software but such analysis is very time consuming and relies on the target code being relatively small, written in an analysable language, compiled with a simple compiler and executed on a predictable CPU with a minimal amount of caching, branch prediction or otherwise complex behaviour. Also, WCET analysis is rarely automatic. Indeed, Ernst et al. [22] note that Cosyma incorrectly predicts the outcome of compiling  $C^X$  code due to the aggressive optimisation routines of the gcc compiler, and this can lead to a design that performs worse than before it was partitioned.

Similarly, it is difficult to accurately predict how large the outcome of hardware synthesis will be without actually performing it. For example, a design that uses many 4-input logic gates will take up more space on an FPGA with only 2-input LUTs than on an FPGA with 4-input LUTs. Without this level of implementation-specific knowledge any utilisation estimates can easily be incorrect. These analysis errors mount as the size of the design increases, making the codesign framework increasingly less effective. Similarly, it can be very difficult to predict the effect of communication and synchronisation delay in a partitioned system, and a few sources of such delay can negate the speed up that would otherwise be gained [61]. Currently, automatic codesign frameworks do not scale to work effectively on systems that are large enough to be of commercial interest. Some of the scalability and tractability problems must be solved before production-level embedded systems can benefit directly from such work.

#### 2.5 Reflection

Computational reflection dates from Brian Smith's work in the early 80s [53] and has been described by Malenfant et al. [42] as a natural extension of the recurring trend in Computer Science to move towards languages with ever later binding times. Reflection is described as:

"...the ability of a program to manipulate as data something representing the state of the program during its own execution. *Introspection* is the ability for a program to observe and therefore reason about its own state. *Intercession* is the ability for a program to modify its own execution state or alter its own interpretation or meaning. Both aspects require a mechanism for encoding execution state as data; providing such an encoding is called *reification*." [15]

There are two commonly identified aspects of reflection; structural reflection and behavioural reflection. Structural reflection allows a program to examine, reason about, and modify its own structure and all the abstract data types it uses. Informally speaking this means it can rewrite its own source code at runtime. Behavioural reflection does not change the actual code but instead affects its meaning and semantics.<sup>4</sup> For example, a C program including the line:

X = 2 \* 3 + 4;

would execute leaving the value of x equal to 10. However, behavioural reflection may alter the language's precedence rules during execution so the meaning of the expression changes, the addition is calculated first and it now evaluates to 14. Alternatively, the meaning of the + symbol may be changed to represent subtraction and so result is evaluation to the value 2.

There does not exist a precise definition of what it means for a language to be reflective. This problem is further compounded by the fact that the implementation of reflection makes use of a number of techniques that existed before reflection became a research topic in its own right. (For example, the ability to manipulate programs as data, to inspect data structures at run-time, and to reason about metaobjects.) Therefore it is impossible to classify a language as reflective purely by considering the techniques it employs. Instead the intent and design goals of the language are often used, with Smalltalk (see section 2.5.1) being a commonly cited example of a language that was designed from the beginning to be reflective.

Absolute reflection is rarely achieved because if the concept is followed as far as theoretically possible the result quickly becomes unmanageable. For example, the

<sup>&</sup>lt;sup>4</sup>As noted by [54] and others, reflection lacks a precise formal definition and so it is likely that the terms used in this section may appear elsewhere in slightly different contexts. This document attempts to use the terms in the most common way that they are presented.

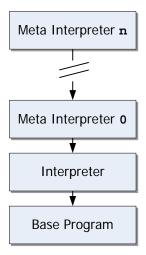

**Figure 2.10:** The Smith and des Rivières reflective tower. Note that these authors used the term 'reflective processor program' rather than interpreter to emphasise that interpretation is not required by reflection.

more powerful aspects of behavioural reflection are commonly implemented using run-time interpretation. However in an entirely reflective language the interpreter itself has a reification which can can be reflected upon. Therefore it becomes possible to create an altered interpreter, which must be run through a lower-level interpreter as a result. However, as this lower-level interpreter also has a reification it is possible to reflect on this also. This results in a theoretically infinite structure called a reflective tower, where each meta-level of interpretation implements the layer below it. Malenfant et al. [42] (see figure 2.10) Whilst a pleasing theoretical concept, it is debatable whether programs can be successfully written to make use of such power. Note that whilst interpretation is used here as an example technique for implementing reflection, it is not required and other methods are available.

There are a number of scenarios that benefit from the use of reflective techniques, but one of the most important is that intercession and behavioural reflection can allow a source language to influence the way in which it is implemented. In languages that support a high degree of reflection, the compiler itself is available to be reflected upon. This allows for a specific function to affect its own compilation and to control the opcodes that are eventually produced from the compilation process. For example, if a normal program is to be executed on a new processor with a custom instruction set then a new compiler would have to be written in order to generate correct object code. However, reflection allows this to be done from the source code level, maybe by simply including a new library that describes the desired instruction set architecture.

Kiczales et al. [37] give a further example of why it can be useful to control a language's implementation. Consider the following two records:

type point is

record

x : Integer;

y : Integer;

end record;

2.5. Reflection

type person is

record

surname : String;

forename : String;

age : Integer;

--Many more data items ... end record;

The point record has only two components and both are always populated with data. As a result its entire storage allocation is always used and access to both items must be fast. The person record however contains many data items which are empty, as the data items that are held on each person are different. Therefore, the record rarely uses its entire space allocation. Whilst the point record would benefit from an internal implementation that uses an array, the person record might be better implemented with a hash table. However, with a fixed language without reflection the compiler will treat both the same and use identical implementations, resulting in a compromise. Reflection allows the programmer to control the implementation style used and thereby increase the efficiency of the final program.

Another situation that benefits from reflection is where a program must interact with previously unseen classes and methods. This could occur in an operating system when it loads new programs, or in a web application that communicates with clients. Introspection makes it possible for the system to examine the available classes and methods of the new code and determine the best way to proceed, without requiring access to source code. It also allows the system to check for potentially unsafe behaviour in new code before executing it.

Reflection also introduces the possibility of runtime self-optimisation. For example, it is possible to create a system that profiles its own execution and reacts to improve its efficiency by altering its own implementation. This allows for a greater range of optimisations than traditional techniques because program flow in a non-reflective language can only diverge at points where the programmer has explicitly defined it (such as at  $i \pm s$  statements). In a reflective system it can happen anywhere. Similarly, reflection is also a powerful technique for implementing Metaobject Protocols (section 2.6 and the Aspect-Oriented Programming paradigm (section 2.7.1).

Clearly the main problem with reflection is that it can become very complex, and it can be difficult to use some of the power that it affords. Also, verification of reflective programs is currently an open problem as it is unclear as to how to reason about source code that can alter itself at any time. [52] Finally, many reflective systems must be interpreted in order to be implemented, which can result in a rather slow implementation. This is not the case for all systems, however, as careful restrictions on the reflective facilities available can allow a system to be compiled.

#### 2.5.1 Smalltalk

Smalltalk<sup>5</sup> is an object-oriented, reflective language that was created at Xerox PARC during the 1970s. It bears a number of conceptual similarities to Lisp in that it is almost entirely written in itself, and is organised using meta-level objects that represent most parts of the language, including the classes, methods, compilers and even stack frames. Smalltalk has one of the most complete sets of reflective facilities of

<sup>&</sup>lt;sup>5</sup>See http://www.smalltalk.org

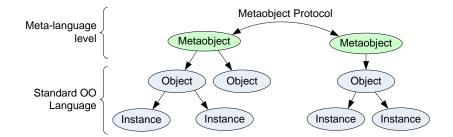

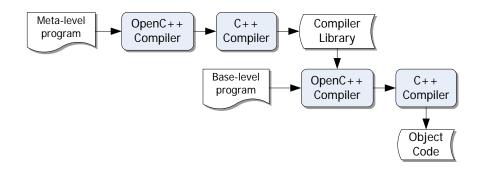

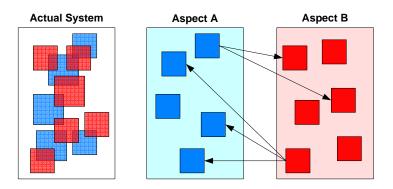

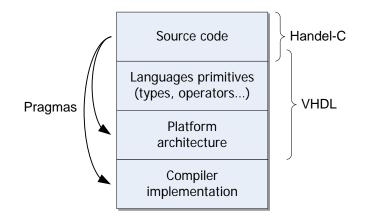

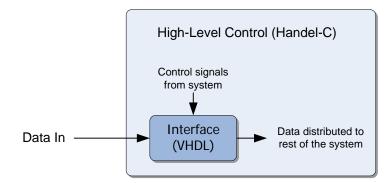

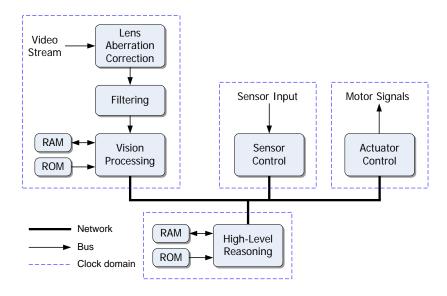

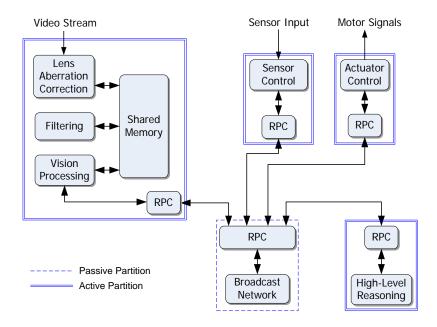

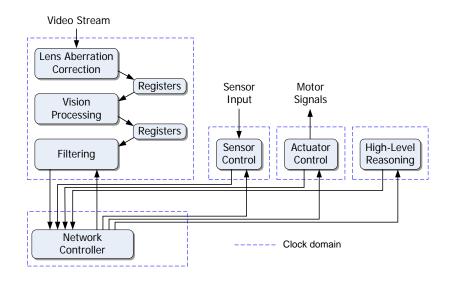

any language in widespread use [51] and only avoids the provision of total reflection because of efficiency reasons.